You are here: Foswiki>DaqSlowControl Web>TDCReadoutBoard>TDCReadoutBoardV2>TRBvIIHowTo>DescriptionOfFPGA (2008-07-23, MarekPalka)Edit Attach

A VIRTEX4 LX40 FPGA is used on the TRBv2.

For writing ./rwv2 w 2 ab 01234567 : where w - mode, 2 -device number(SDRAM), ab- address, 01234567 - value to write Device numbers:

0-FPGA

1-DSP

2-SDRAM

3-Add on board - not existing

4-SFP - not existing

... * Etrax FS and FPGA protocol:

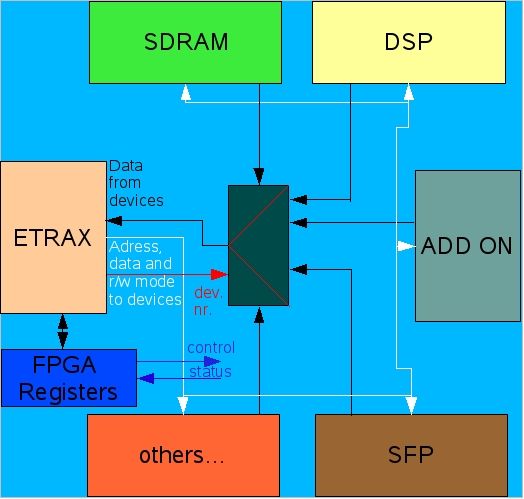

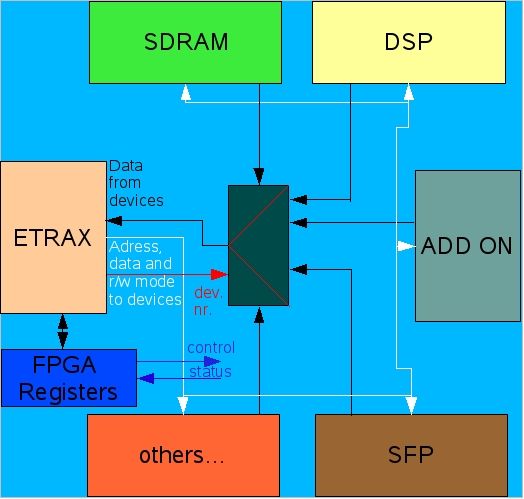

All devices are accessible by the ETRAX-FPGA interface. It can be extended for future needs (add on interface, SFP ...)

* Connection between interfaces:

All devices are accessible by the ETRAX-FPGA interface. It can be extended for future needs (add on interface, SFP ...)

* Connection between interfaces:

FPGA registers

| r/w | adress | bits | |||||||||||||

| r | 0 | 31-26 not used | ADO_LV 25-0 | ||||||||||||

| r | 1 | 31-lvl2 busy | 30:lvl1_fifo_wr_en | 29-16: lvl1_fifo_counter | 15:lvl1 or lvl2_is_busy | 14:lvl1 busy | 13-4:how many words in lvl1 buffer | 3-0:TDCD,C,B,A error | |||||||

| r | 2 | 31-27:not used | 26-24:lvl2_debug:001: IDLE 010: READOUT_WORD1 011: READOUT_WORD2 100: SAVE_EVENT_SIZE 101: SEND_DATA1 |

23-20:LVL1 state: x"1": IDLE x"2"-x"5": SEND_LVL1_TRIGG_1-4 x"6": WAIT_FOR_TOKEN x"7"-x"a": SAVE_ADD_DATA_1-4 x"c": SEND_LVL2_TRIGG |

19-18: delay trigger FSM: 01: IDLE 10: DELAY_1 11: DELAY_2 |

15-0:how many words in event | |||||||||

| r | 3 | 31-0: lvl1_buffer_out | |||||||||||||

| r | 4 | 31-28: not used | 27-24: LVL1 CODE | 23-16: LVL1 TAG | 15-12: not used | 11-8:lvl1_code -internal | 7-0: lvl1 tag minus 1 | ||||||||

| r | 5 | 31-24:how many lvl2 busy ended | 23-16:how many times lvl2 started | 15-8:how many times token was received | 7-0:how many times lvl1 started | ||||||||||

| r/w | 6 | 31-24:additional delay time for trigger to TDC's 10ns resolution | 23-16:how many add data(counters) | 15-10:reserved | 9:eneble SPI for RPC | 8:enable ext. trigger | 7:enable self trigger | 6:enable tdc clock(trbva) | 5:dsp boff(active low) | 4:dsp reset(active low) | 3:dsp bm and bms | 2:enable test signal trigger(2)-100Hz- | 1:enable test signal trigger(1)-100Hz | 0:enable JTAG for TDC | |

| r/w | 7 | 31-12:reserved | 11:spi_cs_d | 10:spi_sdo_d | 9:spi_sck_d | 8:spi_cs_c | 7:spi_sdo_c | 6:spi_sck_c | 5:spi_cs_b | 4:spi_sdo_b | 3:spi_sck_b | 2:spi_cs_a | 1:spi_sdo_a | 0:spi_sck_a | |

| r | 8 | 31-4:reserved | 3:spi_sdi_d | 2:spi_sdi_c | 1:spi_sdi_b | 0:spi_sdi_a | |||||||||

| r/w | e | 31-16:not used | 15-8:trb data version | 7-4:enable test signal b MB3-0 | 3-0:enable test signal a MB3-0 | ||||||||||

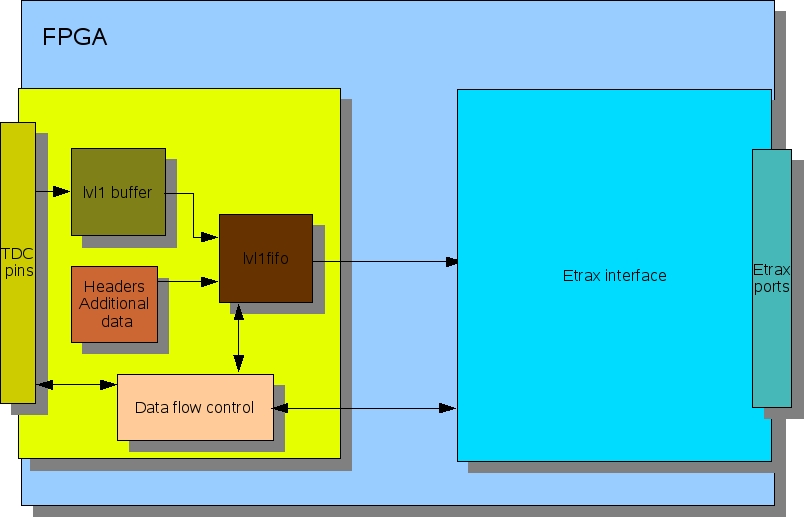

FPGA interfaces

Etrax

The Etrax is sending a mode in which it wants to operate(R/W) with the first strobe. If it is the "read mode" then it sending only 32 bit address,if it is the "write mode" it sends also 32 bit data. To read data from the FPGA registers one has to use the following command: ./rwv2 r 0 1 : where rwv2 is the read write program, r - mode, 0 - which device(FPGA), 1 - address inside the device.For writing ./rwv2 w 2 ab 01234567 : where w - mode, 2 -device number(SDRAM), ab- address, 01234567 - value to write Device numbers:

0-FPGA

1-DSP

2-SDRAM

3-Add on board - not existing

4-SFP - not existing

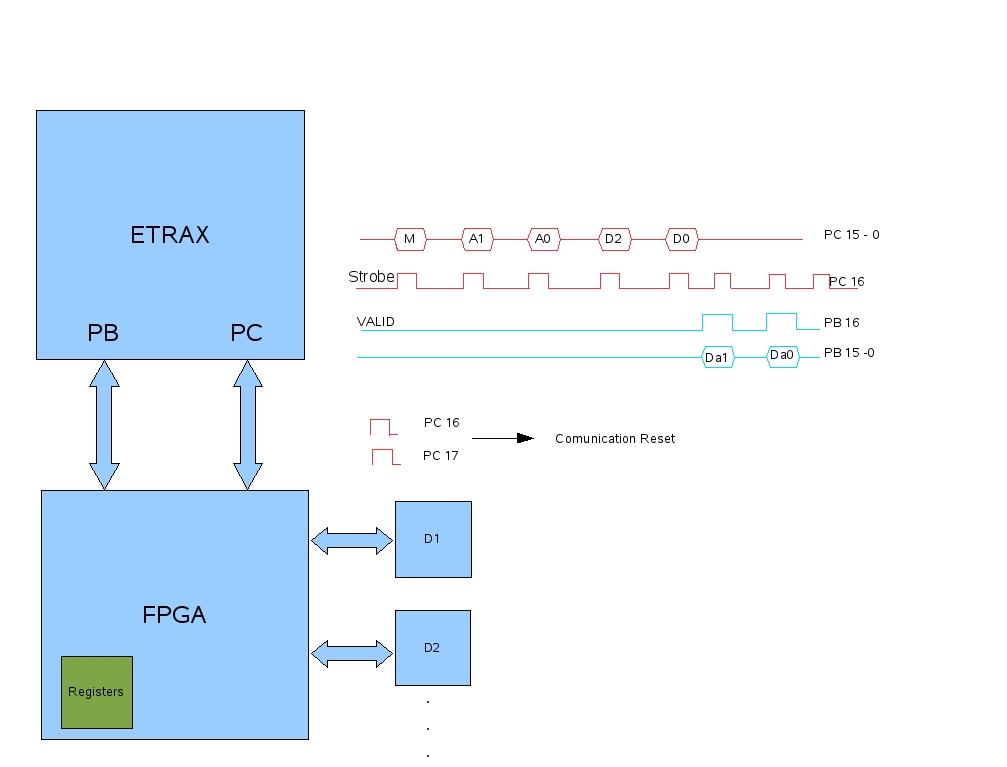

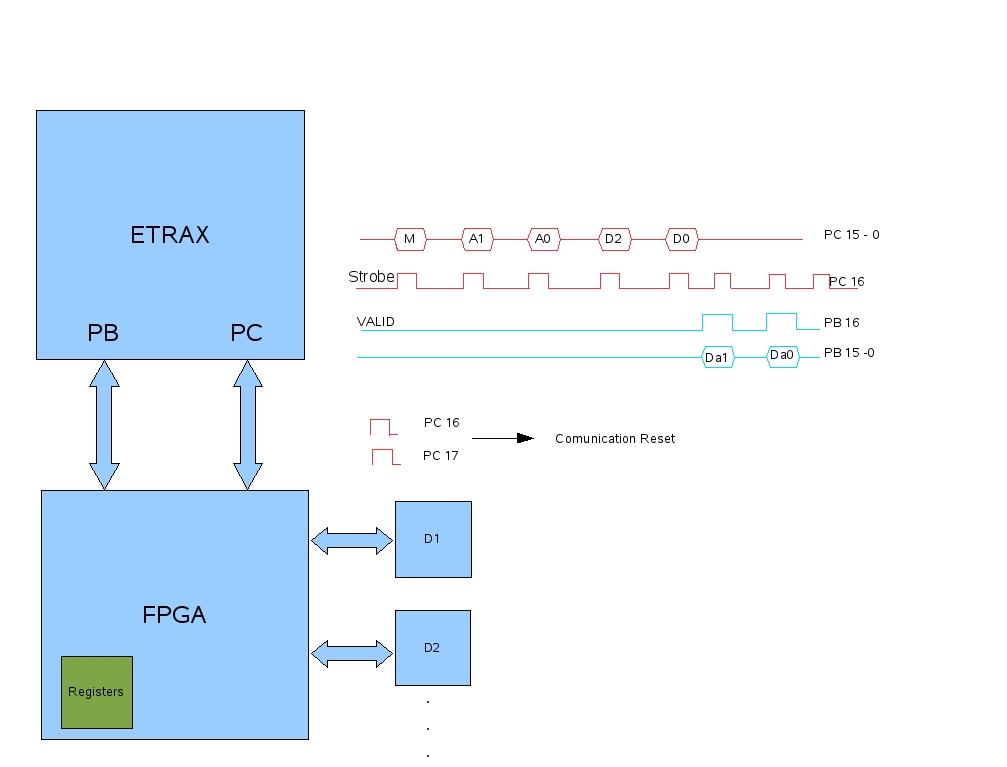

... * Etrax FS and FPGA protocol:

All devices are accessible by the ETRAX-FPGA interface. It can be extended for future needs (add on interface, SFP ...)

* Connection between interfaces:

All devices are accessible by the ETRAX-FPGA interface. It can be extended for future needs (add on interface, SFP ...)

* Connection between interfaces:

DSP

All needed information should be found on: http://www.analog.com/processors/tigersharc/technicalLibrary/manuals/index.html Currently, the DSP interface is used as a host interface between DSP and FPGA. The main signals are HBR - host bus request, HBG - host bus grant, WRL,WRH - write , RD - read, BRST- burst, ACK - acknowledge. To start reading or writing the DSP has to leave the reset state: ./rwv2 w 0 6 30 Then it is possible to write or read: ./rwv2 r 1 0x1xxxxxxx For accessing the Sharc, the offset address is 0x10000000, because the TigerSHARC DSP is a multi processor system (first device).SDRAM

Now it is existing a simple entity just for checking if it is possible to write or read to SDRAM For reading : ./rwv2 r 2 0x110 http://download.micron.com/pdf/datasheets/dram/sdram/512MbSDRAM.pdfTDC

This interface is for downloading the TDC measurements.- Parallel interface:

Optical and SFP

This interface will be use for trb net data transmition (2Gbit). There are entities available which are using this interface. From the SFP one can read out the temperature and the optical power.Addo-on

For controlling and checking the status of add-on boards.VULOM

To be done. -- MarekPalka - 27 Jun 2007| I |

Attachment | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|

| |

inside_fpga.jpg | manage | 92 K | 2007-06-28 - 11:56 | MarekPalka | Connection between interfaces |

| |

protocol_final.jpg | manage | 92 K | 2007-06-27 - 17:30 | MarekPalka | EtraxFS and FPGA protocol |

| |

tdcinterface.jpg | manage | 93 K | 2007-06-28 - 14:58 | MarekPalka | Parallel interface |

Edit | Attach | Print version | History: r8 < r7 < r6 < r5 | Backlinks | View wiki text | Edit wiki text | More topic actions

Topic revision: r8 - 2008-07-23, MarekPalka

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Ideas, requests, problems regarding Foswiki Send feedback | Imprint | Privacy Policy (in German)

Ideas, requests, problems regarding Foswiki Send feedback | Imprint | Privacy Policy (in German)