You are here: Foswiki>DaqSlowControl Web>TDCReadoutBoard>TDCReadoutBoardV2>TRBvIIHowTo>DescriptionOfTDC (2007-07-24, MarekPalka)Edit Attach

TDC is connected with FPGA thru two interfaces:

If one of the TDC's fail then it is possible by putting some jumpers(J24,25,26) and removing resistors(R113,114,115) to exclude this TDC from the chain.

If one of the TDC's fail then it is possible by putting some jumpers(J24,25,26) and removing resistors(R113,114,115) to exclude this TDC from the chain.

For programming TDC and changing settings of TRB refer to the page TDCprogrammingViaJam

- JTAG

- Parallel

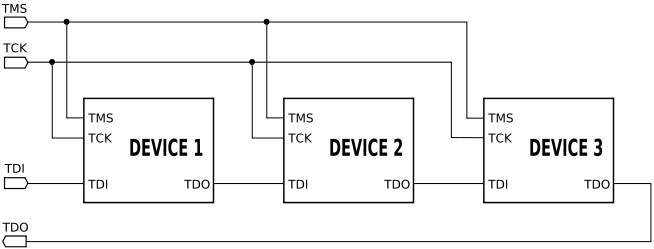

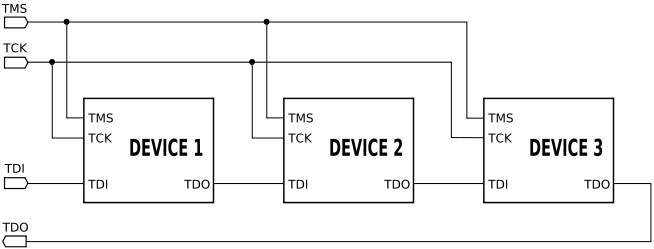

JTAG interface

It is used for programming status register and control register of TDC's. To enable JTAG interface it has to be enabled in FPGA register. ./rwv2 w 0 6 1 After this coresponding lines are connected as below(part of VHDL code):

"... TDC_TMS <= ETRAX_DATA_BUS_C(1);

TDC_TCK <= ETRAX_DATA_BUS_C(2);

TDC_TDI <= ETRAX_DATA_BUS_C(3);

ETRAX_DATA_BUS_C(0) <= TDC_TDO; ..."<BR>

TDC's are in JTAG chain.

* JTAG chain:  If one of the TDC's fail then it is possible by putting some jumpers(J24,25,26) and removing resistors(R113,114,115) to exclude this TDC from the chain.

If one of the TDC's fail then it is possible by putting some jumpers(J24,25,26) and removing resistors(R113,114,115) to exclude this TDC from the chain.For programming TDC and changing settings of TRB refer to the page TDCprogrammingViaJam

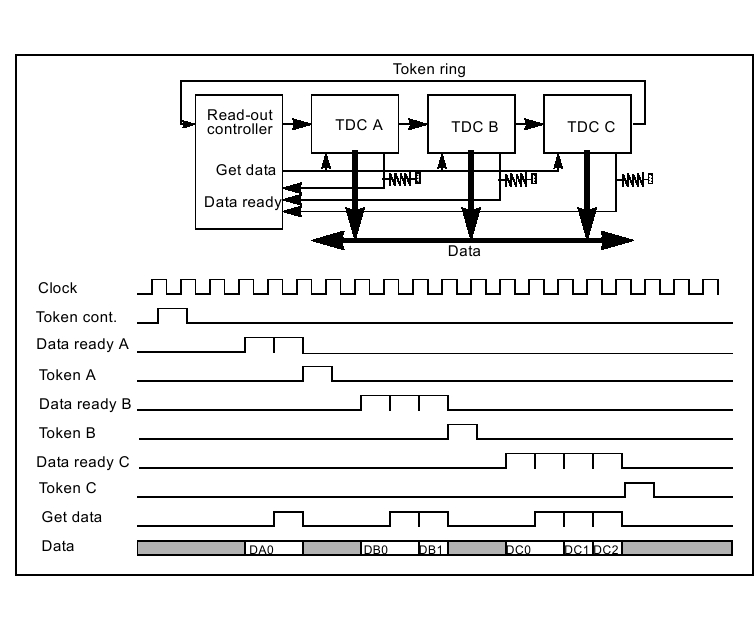

Parallel interface

This interface is used for downloading the data from the TDC. -- MarekPalka - 28 Jun 2007- TDC readout(from hptdc manual):

- hptdc_manual_ver2.2.pdf: hptdc manual

| I |

Attachment | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|

| |

jtagchain.jpg | manage | 25 K | 2007-06-28 - 13:17 | MarekPalka | JTAG chain |

| |

tdcreadout.jpg | manage | 75 K | 2007-06-28 - 13:54 | MarekPalka | TDC readout |

| |

tdcwindows.jpg | manage | 35 K | 2007-06-28 - 13:47 | MarekPalka | Windows in TDC |

| |

hptdc_manual_ver2.2.pdf | manage | 1 MB | 2007-06-28 - 13:58 | MarekPalka | hptdc manual |

Edit | Attach | Print version | History: r3 < r2 < r1 | Backlinks | View wiki text | Edit wiki text | More topic actions

Topic revision: r3 - 2007-07-24, MarekPalka

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Ideas, requests, problems regarding Foswiki Send feedback | Imprint | Privacy Policy (in German)

Ideas, requests, problems regarding Foswiki Send feedback | Imprint | Privacy Policy (in German)