# **Microcomputer Components**

16-Bit CMOS Single-Chip Microcontroller with 128 KByte Flash EPROM

# C167CR-16F

Data Sheet 03.97 Advance Information

## **SIEMENS**

### **Microcomputer Components**

16-Bit CMOS Single-Chip Microcontroller with 128 KByte Flash EPROM

# C167CR-16F

Data Sheet 03.97 Advance Information

| C167CR-16F<br>Revision His |          | Original Version 03.97 (Advance Information) |

|----------------------------|----------|----------------------------------------------|

| Previous Rele              | eases:   | -                                            |

| Page                       | Subjects |                                              |

|                            |          |                                              |

Controller Area Network (CAN): License of Robert Bosch GmbH

### Edition 03.97

### Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation Balanstraße 73, D-81541 München.

© Siemens AG 1997. All Rights Reserved.

As far as patents or other rights of third parties are concerned, liability is only assumed for components per se, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Offices of Siemens Aktiengesellschaft in Germany or the Siemens Companies and Representatives worldwide.

Due to technical requirements components may contain dangerous substances. For information on the type in question please contact your nearest Siemens Office, Components Group.

Siemens AG is an approved CECC manufacturer.

# SIEMENS

### C166-Family of High-Performance CMOS 16-Bit Microcontrollers

### C167CR-16F

### Advance Information C167CR-16F 16-Bit Microcontroller

- High Performance 16-bit CPU with 4-Stage Pipeline

- 100 ns Instruction Cycle Time at 20 MHz CPU Clock

- 500 ns Multiplication (16  $\times$  16 bit), 1  $\mu s$  Division (32 / 16 bit)

- Enhanced Boolean Bit Manipulation Facilities

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Single-Cycle Context Switching Support

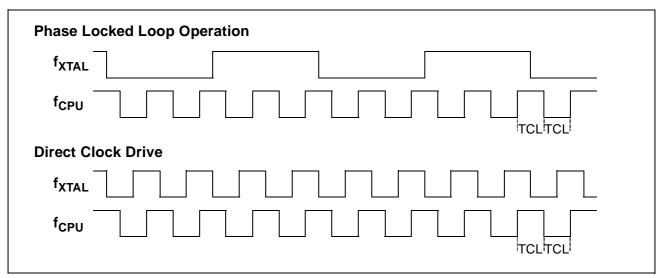

- Clock Generation via on-chip PLL or via direct clock input

- Up to 16 MByte Linear Address Space for Code and Data

- 2 KByte On-Chip Internal RAM (IRAM)

- 2 KByte On-Chip Extension RAM (XRAM)

- 128 KByte On-Chip Flash EPROM with Bank Erase Feature and Read Protection

- Dedicated Flash Control Register with Operation Lock Mechanism

- 12 V External Flash Programming Voltage

- Flash Program Verify and Erase Verify Modes with 1000 Program/Erase Cycles

- Programmable External Bus Characteristics for Different Address Ranges

- 8-Bit or 16-Bit External Data Bus

- Multiplexed or Demultiplexed Address/Data Buses with 5 Programmable Chip-Select Signals

- Hold- and Hold-Acknowledge Bus Arbitration Support

- 1024 Bytes On-Chip Special Function Register Area

- Idle and Power Down Modes

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer via Peripheral Event Controller (PEC)

- 16-Priority-Level Interrupt System with 56 Sources, Sample-Rate down to 50 ns

- 16-Channel 10-bit A/D Converter with 9.7µs Conversion Time

- Two 16-Channel Capture/Compare Units and one 4-Channel PWM Unit

- Two Multi-Functional General Purpose Timer Units with 5 Timers

- Two Serial Channels (Synchronous/Asynchronous and High-Speed-Synchronous)

- On-Chip CAN Interface with 15 Message Objects (Full-CAN/Basic-CAN)

- Programmable Watchdog Timer

- Up to 111 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

- Supported by a Wealth of Development Tools like C-Compilers, Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Bootstrap Loader

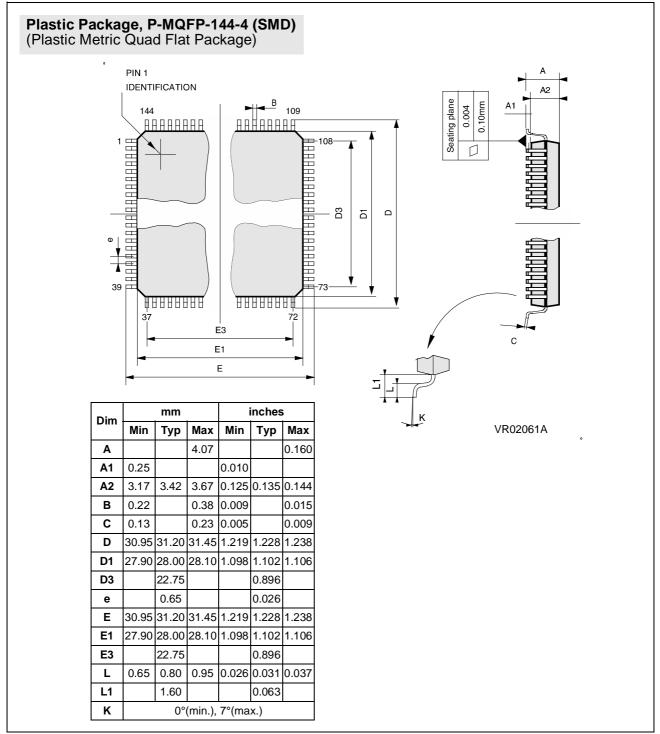

- 144-Pin MQFP Package (EIAJ)

This document describes the  $\ensuremath{\mathsf{SAB-C167CR-16FM}}$  and the  $\ensuremath{\mathsf{SAF-C167CR-16FM}}$  .

For simplicity all versions are referred to by the term C167CR-16F throughout this document.

### Introduction

The C167CR-16F is a new derivative of the Siemens C16x Family of full featured single-chip CMOS microcontrollers. It combines high CPU performance (up to 10 million instructions per second) with high peripheral functionality and enhanced IO-capabilities. It also provides on-chip high-speed RAM, on-chip Flash memory and clock generation via PLL.

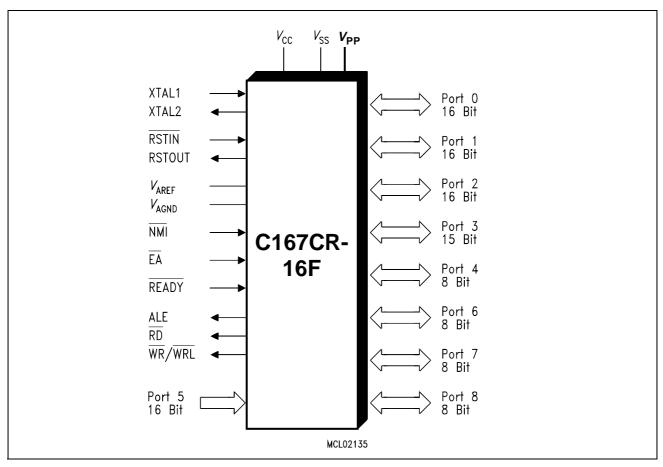

#### Figure 1 Logic Symbol

### **Ordering Information**

The ordering code for Siemens microcontrollers provides an exact reference to the required product. This ordering code identifies:

- the derivative itself, ie. its function set

- the specified temperature range

- the package

- the type of delivery.

For the available ordering codes for the C167CR-16F please refer to the

"Product Information Microcontrollers", which summarizes all available microcontroller variants.

**Note:** The ordering codes for the Mask-ROM versions are defined for each product after verification of the respective ROM code.

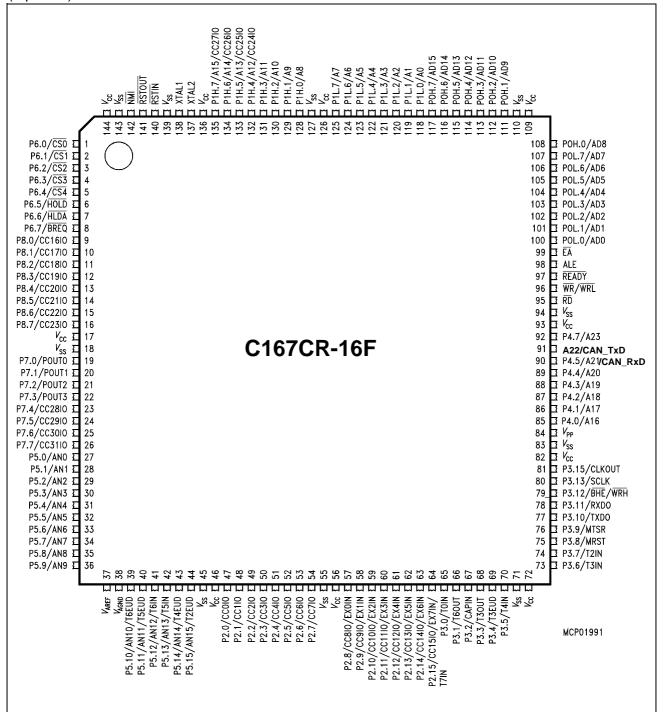

### Pin Configuration

(top view)

Figure 2

### Pin Definitions and Functions

| Symbol         | Pin<br>Number        | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|----------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P6.0 –<br>P6.7 | 1 -<br>8             | 1/0                     | Port 6 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 6 outputs can be configured as push/<br>pull or open drain drivers.<br>The following Port 6 pins also serve for alternate functions:                                                                  |

|                | 1                    | 0                       | P6.0 CS0 Chip Select 0 Output                                                                                                                                                                                                                                                                                                                                                                                          |

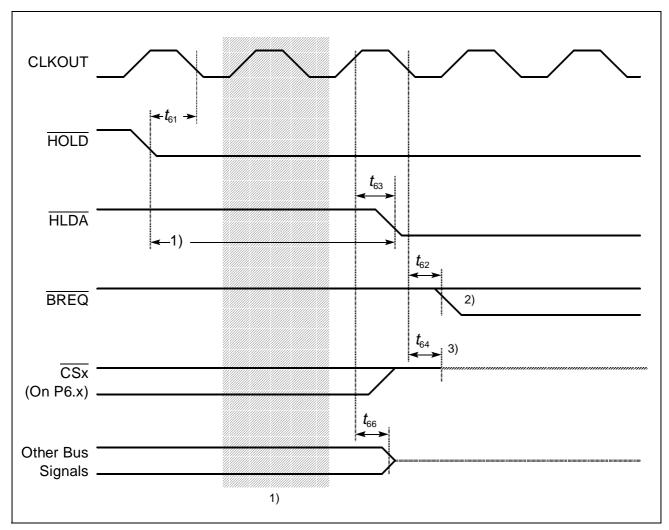

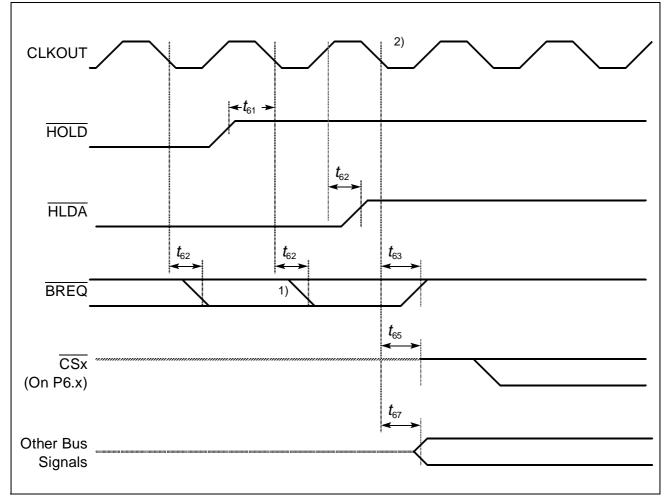

|                | <br>5<br>6<br>7<br>8 | <br>O<br>I<br>O<br>O    | Image: Non-StateImage: Non-StateImage: Non-StateP6.4CS4Chip Select 4 OutputP6.5HOLDExternal Master Hold Request InputP6.6HLDAHold Acknowledge OutputP6.7BREQBus Request Output                                                                                                                                                                                                                                         |

| P8.0 –<br>P8.7 | 9 -<br>16            | I/O                     | Port 8 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 8 outputs can be configured as push/<br>pull or open drain drivers. The input threshold of Port 8 is<br>selectable (TTL or special).<br>The following Port 8 pins also serve for alternate functions: |

|                | 9                    | I/O                     | P8.0 CC16IO CAPCOM2: CC16 CapIn/Comp.Out                                                                                                                                                                                                                                                                                                                                                                               |

|                | <br>16               | <br>I/O                 | P8.7     CC23IO     CAPCOM2: CC23 CapIn/Comp.Out                                                                                                                                                                                                                                                                                                                                                                       |

| P7.0 –<br>P7.7 | 19 -<br>26           | I/O                     | Port 7 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 7 outputs can be configured as push/<br>pull or open drain drivers. The input threshold of Port 7 is<br>selectable (TTL or special).<br>The following Port 7 pins also serve for alternate functions: |

|                | 19                   | 0                       | P7.0 POUT0 PWM Channel 0 Output                                                                                                                                                                                                                                                                                                                                                                                        |

|                | <br>22<br>23         | <br>O<br>I/O            | P7.3POUT3PWM Channel 3 OutputP7.4CC28IOCAPCOM2: CC28 CapIn/Comp.Out                                                                                                                                                                                                                                                                                                                                                    |

|                | <br>26               | <br>I/O                 | P7.7 CC31IO CAPCOM2: CC31 CapIn/Comp.Out                                                                                                                                                                                                                                                                                                                                                                               |

**SIEMENS**

| Symbol | Pin<br>Number | Input (I)<br>Output (O) | Function                                            |                                                       |                                                                                                                                                                                                                                    |

|--------|---------------|-------------------------|-----------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P5.0 – | 27 – 36       | I                       | Port 5 is                                           | a 16-bit                                              | input-only port with Schmitt-Trigger                                                                                                                                                                                               |

| P5.15  | 39 – 44       | I                       | characteris                                         | stics. The p                                          | bins of Port 5 also serve as the (up to 16)                                                                                                                                                                                        |

|        |               |                         | analog in                                           | put channe                                            | els for the A/D converter, where P5.x                                                                                                                                                                                              |

|        |               |                         | equals AN inputs:                                   | Ix (Analog                                            | input channel x), or they serve as timer                                                                                                                                                                                           |

|        | 39            | 1                       | P5.10                                               | T6EUD                                                 | GPT2 Timer T6 Ext.Up/Down Ctrl.Input                                                                                                                                                                                               |

|        | 40            | 1                       | P5.11                                               | T5EUD                                                 | GPT2 Timer T5 Ext.Up/Down Ctrl.Input                                                                                                                                                                                               |

|        | 41            |                         | P5.12                                               | T6IN                                                  | GPT2 Timer T6 Count Input                                                                                                                                                                                                          |

|        | 42            |                         | P5.13                                               | T5IN                                                  | GPT2 Timer T5 Count Input                                                                                                                                                                                                          |

|        | 43            | 1                       | P5.14                                               | T4EUD                                                 | GPT1 Timer T4 Ext.Up/Down Ctrl.Input                                                                                                                                                                                               |

|        | 44            | I                       | P5.15                                               | T2EUD                                                 | GPT1 Timer T2 Ext.Up/Down Ctrl.Input                                                                                                                                                                                               |

| P2.0 – | 47 – 54       | I/O                     | Port 2 is                                           | a 16-bit                                              | bidirectional I/O port. It is bit-wise                                                                                                                                                                                             |

| P2.15  | 57 - 64       |                         | configured<br>impedance<br>pull or op<br>selectable | I as input<br>e state. Po<br>en drain d<br>(TTL or sp | out or output via direction bits. For a pin<br>, the output driver is put into high-<br>rt 2 outputs can be configured as push/<br>rivers. The input threshold of Port 2 is<br>ecial).<br>bins also serve for alternate functions: |

|        | 47            | I/O                     | P2.0                                                | CC0IO                                                 | CAPCOM: CC0 CapIn/Comp.Out                                                                                                                                                                                                         |

|        | <br>54        | <br>I/O                 | <br>P2.7                                            | <br>CC7IO                                             |                                                                                                                                                                                                                                    |

|        | 57            | 1/O<br>1/O              | P2.7<br>P2.8                                        | CC7IO<br>CC8IO                                        | CAPCOM: CC7 CapIn/Comp.Out<br>CAPCOM: CC8 CapIn/Comp.Out,                                                                                                                                                                          |

|        | 57            | I                       | F 2.0                                               | EX0IN                                                 | Fast External Interrupt 0 Input                                                                                                                                                                                                    |

|        | <br>64        | <br>I/O                 | <br>P2.15                                           | <br>CC15IO                                            | <br>CAPCOM: CC15 CapIn/Comp.Out,                                                                                                                                                                                                   |

|        |               |                         | . 2.10                                              | EX7IN                                                 | Fast External Interrupt 7 Input                                                                                                                                                                                                    |

|        |               | I                       |                                                     | T7IN                                                  | CAPCOM2 Timer T7 Count Input                                                                                                                                                                                                       |

### Pin Definitions and Functions (cont'd)

| Symbol         | Pin<br>Number | Input (I)<br>Output (O) | Function                                         |                                                       |                                                                                                                                                                                                                                       |

|----------------|---------------|-------------------------|--------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0 –         | 65 – 70,      | I/O                     | Port 3 is a                                      | a 15-bit (P3                                          | .14 is missing) bidirectional I/O port. It is                                                                                                                                                                                         |

| P3.13,         | 73 – 80,      | I/O                     |                                                  | •                                                     | ble for input or output via direction bits.                                                                                                                                                                                           |

| P3.15          | 81            | I/O                     | •                                                | •                                                     | as input, the output driver is put into high-                                                                                                                                                                                         |

|                | -             |                         | •                                                | •                                                     | rt 3 outputs can be configured as push/                                                                                                                                                                                               |

|                |               |                         | •                                                |                                                       | rivers. The input threshold of Port 3 is                                                                                                                                                                                              |

|                |               |                         |                                                  | (TTL or sp                                            | •                                                                                                                                                                                                                                     |

|                |               |                         |                                                  | · ·                                                   | bins also serve for alternate functions:                                                                                                                                                                                              |

|                | 65            | 1                       | P3.0                                             | TOIN                                                  | CAPCOM Timer T0 Count Input                                                                                                                                                                                                           |

|                | 66            | 0                       | P3.1                                             | T6OUT                                                 | GPT2 Timer T6 Toggle Latch Output                                                                                                                                                                                                     |

|                | 67            |                         | P3.2                                             | CAPIN                                                 | GPT2 Register CAPREL Capture Input                                                                                                                                                                                                    |

|                | 68            | 0                       | P3.3                                             | T3OUT                                                 | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                     |

|                | 69            |                         | P3.4                                             | T3EUD                                                 | GPT1 Timer T3 Ext.Up/Down Ctrl.Input                                                                                                                                                                                                  |

|                | 70            | 1                       | P3.5                                             | T4IN                                                  | GPT1 Timer T4 Input for                                                                                                                                                                                                               |

|                |               |                         | 1 010                                            |                                                       | Count/Gate/Reload/Capture                                                                                                                                                                                                             |

|                | 73            | 1                       | P3.6                                             | T3IN                                                  | GPT1 Timer T3 Count/Gate Input                                                                                                                                                                                                        |

|                | 74            |                         | P3.7                                             | T2IN                                                  | GPT1 Timer T2 Input for                                                                                                                                                                                                               |

|                |               | -                       |                                                  |                                                       | Count/Gate/Reload/Capture                                                                                                                                                                                                             |

|                | 75            | I/O                     | P3.8                                             | MRST                                                  | SSC Master-Rec./Slave-Transmit I/O                                                                                                                                                                                                    |

|                | 76            | 1/O                     | P3.9                                             | MTSR                                                  | SSC Master-Transmit/Slave-Rec. O/I                                                                                                                                                                                                    |

|                | 77            | 0                       | P3.10                                            | T×D0                                                  | ASC0 Clock/Data Output (Asyn./Syn.)                                                                                                                                                                                                   |

|                | 78            | I/O                     | P3.11                                            | R×D0                                                  | ASC0 Data Input (Asyn.) or I/O (Syn.)                                                                                                                                                                                                 |

|                | 79            | 0                       | P3.12                                            | BHE                                                   | Ext. Memory High Byte Enable Signal,                                                                                                                                                                                                  |

|                |               | 0                       |                                                  | WRH                                                   | Ext. Memory High Byte Write Strobe                                                                                                                                                                                                    |

|                | 80            | I/O                     | P3.13                                            | SCLK                                                  | SSC Master Clock Outp./Slave Cl. Inp.                                                                                                                                                                                                 |

|                | 81            | 0                       | P3.15                                            | CLKOUT                                                | System Clock Output (=CPU Clock)                                                                                                                                                                                                      |

| P4.0 –<br>P4.7 | 85 - 92<br>85 | I/O<br>O                | programm<br>configured<br>impedanc<br>In case of | hable for inp<br>d as input<br>e state.<br>an externa | bidirectional I/O port. It is bit-wise<br>but or output via direction bits. For a pin<br>, the output driver is put into high-<br>I bus configuration, Port 4 can be used to<br>ddress lines:<br>Least Significant Segment Addr. Line |

|                |               |                         |                                                  |                                                       |                                                                                                                                                                                                                                       |

|                | 89            | 0                       | P4.4                                             | A20                                                   | Segment Address Line                                                                                                                                                                                                                  |

|                | 90            | 0                       | P4.5                                             | A21                                                   | Segment Address Line,                                                                                                                                                                                                                 |

|                |               |                         |                                                  |                                                       | CAN Receive Data Input                                                                                                                                                                                                                |

|                | 91            | 0                       | P4.6                                             | A22                                                   | Segment Address Line,                                                                                                                                                                                                                 |

|                |               | 0                       |                                                  |                                                       | CAN Transmit Data Output                                                                                                                                                                                                              |

|                | 92            | 0                       | P4.7                                             | A23                                                   | Most Significant Segment Addr. Line                                                                                                                                                                                                   |

| RD             | 95            | 0                       |                                                  | •                                                     | ead Strobe. $\overline{RD}$ is activated for every r data read access.                                                                                                                                                                |

### Pin Definitions and Functions (cont'd)

**SIEMENS**

| Symbol                                          | Pin<br>Number                   | Input (I)<br>Output (O) | Function                                                                                                                     |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                 |  |

|-------------------------------------------------|---------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| WR/<br>WRL                                      | 96                              | 0                       | activated for every ex<br>this pin is activated for<br>bit bus, and for every                                                | External Memory Write Strobe. In WR-mode this pi<br>activated for every external data write access. In WRL-m<br>this pin is activated for low byte data write accesses on a<br>bit bus, and for every data write access on an 8-bit bus.<br>WRCFG in register SYSCON for mode selection. |                                                                                                                                                                                                                                 |  |

| READY                                           | 97                              | 1                       | level at this pin durin                                                                                                      | ng an external me<br>nory cycle time v                                                                                                                                                                                                                                                   | on is enabled, a high<br>emory access will force<br>vaitstates until the pin                                                                                                                                                    |  |

| ALE                                             | 98                              | 0                       |                                                                                                                              | al memory or an                                                                                                                                                                                                                                                                          | e used for latching the address latch in the                                                                                                                                                                                    |  |

| ĒĀ                                              | 99                              | 1                       | External Access Enal<br>after Reset forces the<br>execution out of exter<br>execution out of the i                           | C167CR-16F to rnal memory. A hi                                                                                                                                                                                                                                                          | gh level forces                                                                                                                                                                                                                 |  |

| PORT0:<br>P0L.0 –<br>P0L.7,<br>P0H.0 -<br>P0H.7 | 100 –<br>107<br>108,<br>111-117 | I/O                     | and P0H. It is bit-wis<br>direction bits. For a p<br>is put into high-impeo<br>In case of an extern<br>the address (A) and a | se programmable<br>bin configured as<br>dance state.<br>al bus configurati<br>address/data (AD)<br>ta (D) bus in demi<br><b>modes:</b><br>8-bit<br>D0 – D7<br>I/O                                                                                                                        | rectional I/O ports P0L<br>for input or output via<br>input, the output driver<br>ion, PORT0 serves as<br>bus in multiplexed bus<br>ultiplexed bus modes.<br>16-bit<br>D0 - D7<br>D8 - D15<br>16-bit<br>AD0 - AD7<br>AD8 - AD15 |  |

| Pin | Definitions | and | Functions | (cont'd) |

|-----|-------------|-----|-----------|----------|

|-----|-------------|-----|-----------|----------|

| Symbol     | Pin<br>Number | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PORT1:     |               | I/O                     | PORT1 consists of the two 8-bit bidirectional I/O ports P1L                                                                                                                                                                                                                                                                                                                                                 |

| P1L.0 –    | 118 –         |                         | and P1H. It is bit-wise programmable for input or output via                                                                                                                                                                                                                                                                                                                                                |

| P1L.7,     | 125           |                         | direction bits. For a pin configured as input, the output driver                                                                                                                                                                                                                                                                                                                                            |

| P1H.0 -    | 128 –         |                         | is put into high-impedance state. PORT1 is used as the 16-bit                                                                                                                                                                                                                                                                                                                                               |

| P1H.7      | 135           |                         | address bus (A) in demultiplexed bus modes and also after<br>switching from a demultiplexed bus mode to a multiplexed bus<br>mode.<br>The following PORT1 pins also serve for alternate functions:                                                                                                                                                                                                          |

|            | 132           | 1                       | P1H.4 CC24IO CAPCOM2: CC24 Capture Input                                                                                                                                                                                                                                                                                                                                                                    |

|            | 133           | 1                       | P1H.5 CC25IO CAPCOM2: CC25 Capture Input                                                                                                                                                                                                                                                                                                                                                                    |

|            | 134           | 1                       | P1H.6 CC26IO CAPCOM2: CC26 Capture Input                                                                                                                                                                                                                                                                                                                                                                    |

|            | 135           | I                       | P1H.7 CC27IO CAPCOM2: CC27 Capture Input                                                                                                                                                                                                                                                                                                                                                                    |

| XTAL1      | 138           | I                       | XTAL1: Input to the oscillator amplifier and input to the internal clock generator                                                                                                                                                                                                                                                                                                                          |

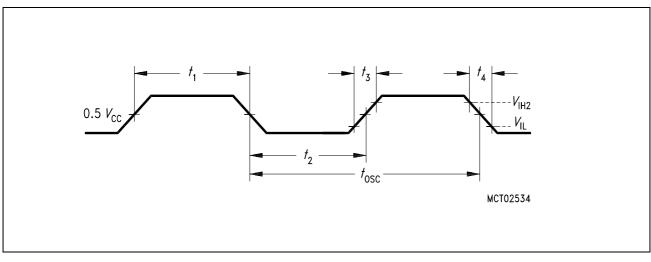

| XTAL2      | 137           | 0                       | XTAL2: Output of the oscillator amplifier circuit.<br>To clock the device from an external source, drive XTAL1,<br>while leaving XTAL2 unconnected. Minimum and maximum<br>high/low and rise/fall times specified in the AC Characteristics<br>must be observed.                                                                                                                                            |

| RSTIN      | 140           | 1                       | Reset Input with Schmitt-Trigger characteristics. A low level at this pin for a specified duration while the oscillator is running resets the C167CR-16F. An internal pullup resistor permits power-on reset using only a capacitor connected to $V_{\rm SS}$ .                                                                                                                                             |

| RSTOUT     | 141           | 0                       | Internal Reset Indication Output. This pin is set to a low level<br>when the part is executing either a hardware-, a software- or a<br>watchdog timer reset. RSTOUT remains low until the EINIT<br>(end of initialization) instruction is executed.                                                                                                                                                         |

| NMI        | 142           | 1                       | Non-Maskable Interrupt Input. A high to low transition at this pin causes the CPU to vector to the NMI trap routine. When the PWRDN (power down) instruction is executed, the NMI pin must be low in order to force the C167CR-16F to go into power down mode. If NMI is high, when PWRDN is executed, the part will continue to run in normal mode. If not used, pin NMI should be pulled high externally. |

| $V_{AREF}$ | 37            | -                       | Reference voltage for the Analog/Digital converter.                                                                                                                                                                                                                                                                                                                                                         |

| $V_{AGND}$ | 38            | -                       | Reference ground for the Analog/Digital converter.                                                                                                                                                                                                                                                                                                                                                          |

| Symbol          | Pin<br>Number                                             | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                   |

|-----------------|-----------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PP</sub> | 84                                                        | -                       | Flash programming voltage.<br>This pin accepts the programming/erase voltage for the C167CR-16F ( $V_{PP} = 12$ V).<br>During normal operation (programming voltage $V_{PP} = 12$ V not required) this pin must be connected to $V_{CC}$ . |

| V <sub>cc</sub> | 17, 46,<br>56, 72,<br>82, 93,<br>109,<br>126,<br>136, 144 | -                       | Digital Supply Voltage:<br>+ 5 V during normal operation and idle mode.<br>≥ 2.5 V during power down mode.                                                                                                                                 |

| V <sub>SS</sub> | 18, 45,<br>55, 71,<br>83, 94,<br>110,<br>127,<br>139, 143 | -                       | Digital Ground.                                                                                                                                                                                                                            |

### Pin Definitions and Functions (cont'd)

**Note:** All  $V_{SS}$  pins and all  $V_{CC}$  pins must be connected to the system ground and the power supply, respectively.

### **Functional Description**

This document only describes specific properties of the C167CR-16F, eg. Flash memory functionality or specific DC and AC Characteristics, while for all other descriptions common for the C167CR-16F and the C167CR, eg. functional description, it refers to the respective Data Sheet for the Non-Flash device.

A detailled description of the C167CR-16F's instruction set can be found in the "C16x Family Instruction Set Manual".

### **Memory Organization**

The memory space of the C167CR-16F is configured in a Von Neumann architecture which means that code memory, data memory, registers and I/O ports are organized within the same linear address space which includes 16 MBytes. The entire memory space can be accessed bytewise or wordwise. Particular portions of the on-chip memory have additionally been made directly bitaddressable.

2 KBytes of on-chip Internal RAM are provided as a storage for user defined variables, for the system stack, general purpose register banks and even for code. A register bank can consist of up to 16 wordwide (R0 to R15) and/or bytewide (RL0, RH0, ..., RL7, RH7) so-called General Purpose Registers (GPRs).

1024 bytes (2 \* 512 bytes) of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are wordwide registers which are used for controlling and monitoring functions of the different on-chip units. Unused SFR addresses are reserved for future members of the C16x family.

2 KBytes of on-chip Extension RAM (XRAM) are provided to store user data, user stacks or code. The XRAM is accessed like external memory and therefore cannot be used for the system stack or for register banks and is not bitadressable. The XRAM allows 16-bit accesses with maximum speed.

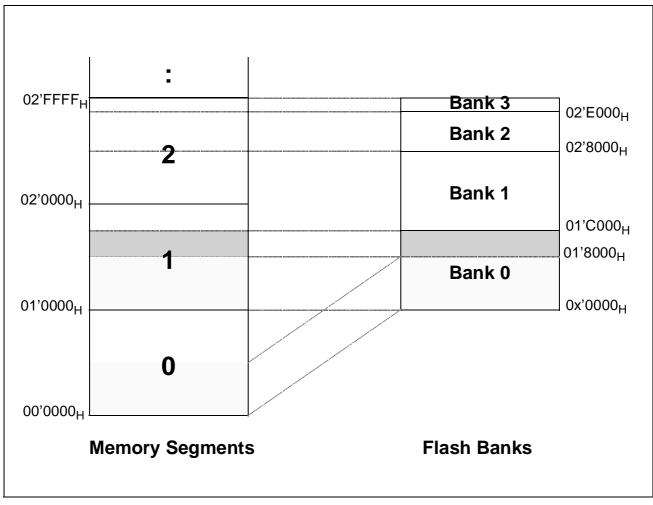

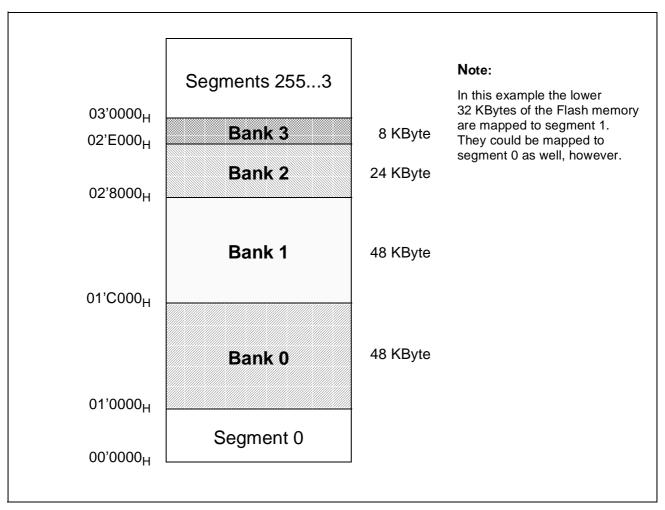

128 KBytes of on-chip Flash memory are provided to store user code or (read only) data. The Flash memory is divided into 4 blocks of different size which can be programmed/erased separately.

In order to meet the needs of designs where more memory is required than is provided on chip, up to 16 MBytes of external RAM and/or ROM can be connected to the microcontroller.

### **Flash Memory Overview**

The C167CR-16F provides 128 KBytes of electrically erasable and reprogrammable non-volatile Flash EPROM on-chip for code or constant data.

A separate Flash Control Register (FCR) has been implemented to control Flash operations like programming or erasure. For programming or erasing an external 12 V programming voltage must be applied to the VPP pin. Flash programming and erasure is only possible during writing mode which is entered via a special key code sequence (Unlock sequence) to avoid unintended Flash operations.

The Flash memory is organized in blocks 32 bits wide which allows even double-word instructions to be fetched in just one machine cycle. The entire Flash memory is divided into four blocks with different sizes (48/48/24/8 KByte). This allows to erase each block separately, when only parts of the Flash memory need to be reprogrammed. Word or double word programming typically takes 100  $\mu$ s, block erasing typically takes 1 s (@ 20 MHz CPU clock). The Flash memory features a typical endurance of 1000 erasing/programming cycles. Erased Flash memory cells contain all '1's, as known from standard EPROMs.

The Flash memory can be programmed both in an appropriate programming board and in the target system which provides a lot of flexibility. The C167CR-16F's on-chip bootstrap loader may be used to load and start the programming code. Any code that programs or erases Flash memory locations must be executed from memory outside the on-chip Flash memory itself (on-chip RAM or external memory).

To save the customer's know-how, a Flash memory protection option is provided in the C167CR-16F. If this was activated once, Flash memory contents cannot be read from any location outside the Flash memory itself (see section "Flash Protection").

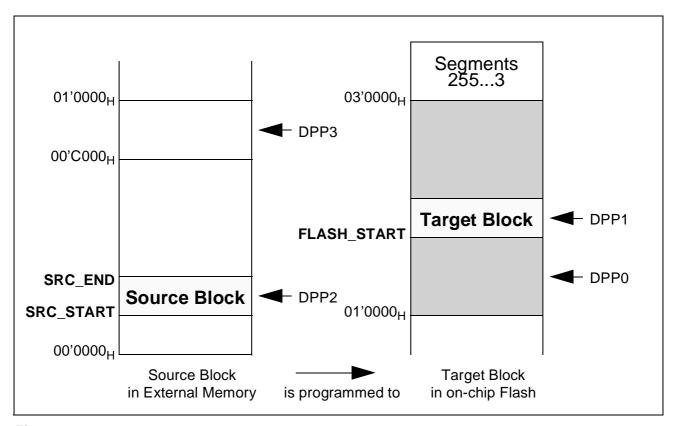

The lower 32 KBytes of the on-chip Flash memory of the C167CR-16F can be mapped to either segment 0 ( $00'0000_H$  to  $00'7FFF_H$ ) or segment 1 ( $01'0000_H$  to  $01'7FFF_H$ ) during the initialization phase to allow external memory to be used for additional system flexibility. The upper 96 KBytes of the on-chip Flash memory are assigned to locations  $01'8000_H$  to  $02'FFF_H$ .

In standard mode (the normal operating mode) the Flash memory appears like the standard on-chip ROM of C167 devices with the same timing and functionality. Instruction fetches and data operand reads are performed with all addressing modes of the C16x instruction set.

In writing mode specific blocks of the on-chip Flash memory can be programmed (doublewords or words) or erased (banks). Writing mode is entered via a special key lock sequence and provides full access to the Flash Control Register (FCR). For programming as well as for erasing there are specific verify modes that allow to validate the previous operation in order to ensure secure Flash handling.

The following terminology is used in this document:

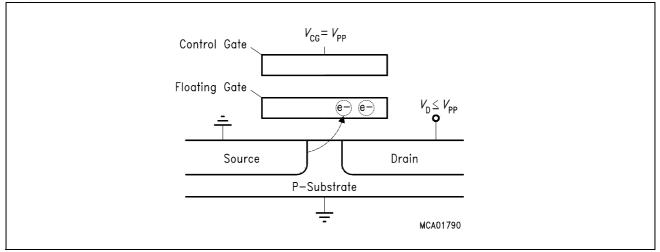

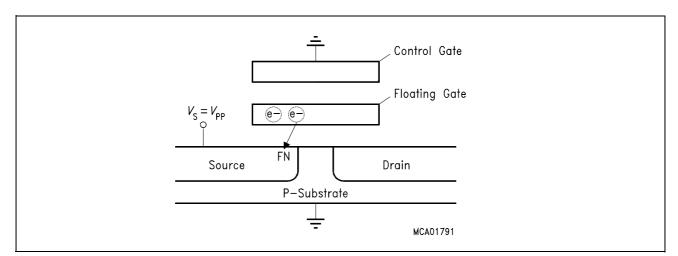

Flash **WRITING** means changing the state of the floating gate. Flash **PROGRAMMING** means loading electrons onto the floating gate. Flash **ERASING** means removing electrons from the floating gate.

Please refer to section "Fundamentals of Flash Technology".

### C167CR-16F

**SIEMENS**

Figure 3 Flash Memory Overview

### **Flash Memory Configuration**

Upon reset the default memory configuration of the C167CR-16F is determined by the state of its  $\overline{EA}$  pin. When  $\overline{EA}$  is high the startup code is fetched from the on-chip Flash memory, when  $\overline{EA}$  is low the internal ROM is disabled and the startup code is fetched from external memory.

In order to access the on-chip Flash memory after booting from external memory the internal ROM must be enabled via software by setting bit ROMEN in register SYSCON. The lower 32 KBytes of the Flash memory can be mapped to segment 0 or to segment 1, controlled by bit ROMS1 in register SYSCON. Mapping to segment 1 preserves the external memory containing the startup code, while mapping to segment 0 replaces the lower 32 KBytes of the external memory with on-chip Flash memory. In this case a valid vector table must be provided. As the on-chip Flash memory covers more than segment 0 segmentation should be enabled (by clearing bit SGTDIS in register SYSCON) in order to ensure correct stack handling when branching to the upper segments.

Whenever the internal memory configuration of the C167CR-16F is changed (enable, disable, mapping) the following procedure must be used to ensure correct operation:

- Configure the internal ROM as required

- Execute an inter-segment branch (JMPS, CALLS, RETS)

- Reload all four DPP registers

- **Note:** Instructions that configure the internal ROM may only be executed from internal RAM or from external memory, **not** from the ROM itself. Register SYSCON can only be modified **before** the execution of the EINIT instruction.

The C167CR-16F's Bootstrap Loader provides a mechanism to load the startup code and/or the Flash progamming routines from a remote code source via the serial interface without requiring additional external memory. This allows for firmware updates of the Flash memory for program and/ or data values.

### The Flash Control Register (FCR)

In standard operation mode the Flash memory can be accessed like the normal maskprogrammable on-chip ROM of the C167CR. So all appropriate direct and indirect addressing modes can be used for reading the Flash memory.

All programming or erase operations of the Flash memory are controlled via the 16-bit Flash Control Register FCR. To prevent unintentional writing to the Flash memory the FCR is locked and inactive during standard operation mode. Before a valid access to the FCR is enabled, the Flash memory writing mode must be entered. This is done via a special key code instruction sequence.

**Note:** The FCR is no real register (SFR or GPR) but is rather virtually mapped into the active address space of the Flash memory. All even direct (mem) word accesses refer to the FCR (no byte- or bit-addressing), while all indirect ([Rw<sub>n</sub>]) accesses refer to the Flash memory array itself. ROM mapping and DPP referencing must be considered for FCR accesses.

### FCR (Even Flash Address)

### Reset Value: 00X0<sub>H</sub>\*)

| 15         | 14  | 13 | 12                                                                                                                                                                          | 11                                                                                                                   | 10       | 9                                                                                               | 8     | 7                                | 6  | 5   | 4          | 3         | 2              | 1   | 0   |

|------------|-----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------|-------|----------------------------------|----|-----|------------|-----------|----------------|-----|-----|

| FWM<br>SET | -   | -  | -                                                                                                                                                                           | -                                                                                                                    | -        | В                                                                                               | E     | WDW<br>W                         | СК | CTL | VPP<br>REV | FC<br>VPP | FBUSY<br>RPROT | FEE | FWE |

| rw         | rw  | rw | rw                                                                                                                                                                          | rw                                                                                                                   | rw       | r١                                                                                              | N     | rw                               | r١ | N   | r          | rw        | r/w            | rw  | rw  |

| Bit        |     |    | Functi                                                                                                                                                                      | on                                                                                                                   |          |                                                                                                 |       |                                  |    |     |            |           |                |     |     |

| FWE        |     |    | 0: F                                                                                                                                                                        |                                                                                                                      |          |                                                                                                 |       |                                  |    |     |            |           |                |     |     |

| FEE        |     |    | 0: F                                                                                                                                                                        | Flash Erase Enable Bit (Significant only, when FWE='1', see description below)<br>0: Flash programming mode selected |          |                                                                                                 |       |                                  |    |     |            |           |                |     |     |

| FBUS       | Ϋ́  |    |                                                                                                                                                                             | lo Flas                                                                                                              | sh write | e oper                                                                                          | ation | sses)<br>in prog<br>progres:     |    |     |            |           |                |     |     |

| RPRO       | т   |    |                                                                                                                                                                             | eactiv                                                                                                               | ates F   | lash re                                                                                         | ead p | ation B<br>protection<br>ection, | n  |     |            | ses)      |                |     |     |

| FCVP       | Ρ   |    | Flash Control V <sub>PP</sub> Bit0 : No V <sub>PP</sub> failure occurred during a Flash write operation1 : V <sub>PP</sub> failure occurred during a Flash write operation  |                                                                                                                      |          |                                                                                                 |       |                                  |    |     |            |           |                |     |     |

| VPPR       | EV  |    | Flash V <sub>PP</sub> Revelation Bit         0 : No valid V <sub>PP</sub> applied to pin V <sub>PP</sub> 1 : V <sub>PP</sub> applied to pin V <sub>PP</sub> is valid        |                                                                                                                      |          |                                                                                                 |       |                                  |    |     |            |           |                |     |     |

| СКСТ       | Ľ   |    | Internal Flash Timer Clock Control<br>Determines the width of an internal Flash write or erase pulse                                                                        |                                                                                                                      |          |                                                                                                 |       |                                  |    |     |            |           |                |     |     |

| WDW        | W   |    | <ul> <li>Word / Double Word Writing Bit (significant only in programming mode)</li> <li>0: 16-bit programming operation</li> <li>1: 32-bit programming operation</li> </ul> |                                                                                                                      |          |                                                                                                 |       |                                  |    |     |            |           |                |     |     |

| BE         |     |    | Bank Erase Select (significant only in erasing mode)<br>Selects the Flash Bank to be erased                                                                                 |                                                                                                                      |          |                                                                                                 |       |                                  |    |     |            |           |                |     |     |

| FWMS       | SET |    | 0: E                                                                                                                                                                        | xit Fla                                                                                                              | sh wri   | ode Set Bit (see description below)<br>writing mode, return to standard mode<br>sh writing mode |       |                                  |    |     |            |           |                |     |     |

\*) The reset value of bit VPPREV depends on the voltage on pin  $V_{\mbox{\scriptsize PP}}.$

**The selection of Flash Operation and Read Mode** is done via the three bits FWE, FEE and FWMSET. The table below shows the combinations for these bits to select a specific function:

| FWMSET | FEE | FWE | Flash Operation Mode | Flash Read Mode              |

|--------|-----|-----|----------------------|------------------------------|

| 1      | 1   | 1   | Erasing mode         | Erase-Verify-Read via [Rn]   |

| 1      | 0   | 1   | Programming mode     | Program-Verify-Read via [Rn] |

| 1      | Х   | 0   | Non-Verify mode      | Normal Read via [Rn]         |

| 0      | Х   | Х   | Standard mode        | Normal Read via [Rn] or mem  |

FWE enables/disables write operations, FEE selects erasing or programming, FWMSET indicates writing mode and is set automatically once the writing mode is entered. Bits FWE and FEE select an operation, but do not directly execute this operation.

**Note:** Watch the FWMSET bit when writing to register FCR (word access only) in order not to exit Flash writing mode unintentionally by clearing bit FWMSET.

**FBUSY:** This **read-only flag** is set to '1' while a Flash programming or erasing operation is in progress. FBUSY is set via hardware when the respective program/erase command is issued.

**RPROT:** This **write-only** Flash **Read Protection** bit determines whether Flash protection is active or inactive. RPROT is the only FCR bit which can be modified even in the Flash standard mode but only by an instruction executed from the on-chip Flash memory itself. Per reset, RPROT is set to '1'.

Note: RPROT is only significant if the general Flash memory protection is enabled.

**FCVPP and VPPREV:** These **read-only** bits allow to monitor the  $V_{PP}$  voltage. The Flash **Vpp Revelation** bit VPPREV reflects the state of the  $V_{PP}$  voltage in the Flash writing mode (VPPREV = '0' indicates that  $V_{PP}$  is below the threshold value necessary for reliable programming or erasure, otherwise VPPREV = '1'). The **Flash Control**  $V_{PP}$  bit FCVPP indicates if  $V_{PP}$  fell below the valid threshold value during a Flash programming or erase operation (FCVPP = '1') and the operation therefore might not have been executed properly. FCVPP = '0' after such an operation indicates that no critical discontinuity on  $V_{PP}$  has occurred.

**CKCTL:** This **Flash Timer Clock Control** bitfield controls the width of the programming or erase pulses (TPRG) applied to Flash memory cells during the corresponding operation. The width of a single programming or erase pulse and the cumulated programming or erase time must not exceed certain values to avoid putting the Flash memory under critical stress (see table below). The pulse width and also the maximum number on programming or erase attempts allowed depends on the CPU clock frequency.

| Time Specification                 | Limit Value |  |  |  |

|------------------------------------|-------------|--|--|--|

| Maximum Programming Pulse Width    | 200 μs      |  |  |  |

| Maximum Cumulated Programming Time | 2.5 ms      |  |  |  |

| Maximum Erase Pulse Width          | 20 ms       |  |  |  |

| Maximum Cumulated Erase Time       | 30 s        |  |  |  |

| Setting of<br>CKCTL | Length of<br>TPRG                    | TPRG<br>@ f <sub>CPU</sub> = 20 MHz | f <sub>CPUmin</sub><br>for programming | f <sub>CPUmin</sub><br>for erasing |

|---------------------|--------------------------------------|-------------------------------------|----------------------------------------|------------------------------------|

| 0 0                 | 2 <sup>8</sup> * 1/f <sub>CPU</sub>  | 12.8 µs                             | 1.28 MHz                               | ( 12.8 KHz) <sup>1)</sup>          |

| 0 1                 | 2 <sup>11</sup> * 1/f <sub>CPU</sub> | 102.4 µs                            | 10.24 MHz                              | ( 102.4 KHz) <sup>1)</sup>         |

| 10                  | 2 <sup>15</sup> * 1/f <sub>CPU</sub> | 1.64 ms                             |                                        | 1.64 MHz                           |

| 11                  | 2 <sup>18</sup> * 1/f <sub>CPU</sub> | 13.11 ms                            |                                        | 13.11 MHz                          |

In order not to exceed the limit values listed above, a specific CKCTL setting requires a minimum CPU clock frequency, as listed below.

<sup>1)</sup> Please note that these are computed values. Actual values must respect the operational range specified for the C167CR-16F.

The maximum number of allowed programming or erase attempts depends on the CPU clock frequency and on the CKCTL setting chosen in turn. This number results from the actual pulse width compared to the maximum pulse width (see above tables).

The table below lists some sample frequencies, the respective recommended CKCTL setting and the resulting maximum number of program / erase pulses:

| f <sub>CPU</sub> | Programming |         | g Erasing            |       |         |                       |

|------------------|-------------|---------|----------------------|-------|---------|-----------------------|

|                  | CKCTL       | TPROG   | N <sub>PROGmax</sub> | CKCTL | TPROG   | N <sub>ERASEmax</sub> |

| 1 MHz            | 0 0         | 128 µs  | 19                   | 0 1   | 2.05 ms | 14648                 |

| 10 MHz           | 0 0         | 12.8 µs | 195                  | 1 0   | 3.28 ms | 9155                  |

| 16 MHz           | 0 0         | 8 µs    | 312                  | 1 0   | 2.05 ms | 14648                 |

| 20 MHz           | 0 0         | 6.4 µs  | 390                  | 1 0   | 1.64 ms | 18310                 |

**BE:** The Flash **Bank Erasing** bit field determines the Flash memory bank to be erased (see table below). The physical addresses of the lower 32 KBytes of bank 0 depend on the Flash memory mapping chosen.

| BE setting | Bank | Size  | Addresses Selected for Erasure (x = 0 or 1)                                                 |

|------------|------|-------|---------------------------------------------------------------------------------------------|

| 0 0        | 0    | 48 KB | 0x'0000 <sub>H</sub> to 0x'7FFF <sub>H</sub> / 01'8000 <sub>H</sub> to 01'BFFF <sub>H</sub> |

| 0 1        | 1    | 48 KB | 01'C000 <sub>H</sub> to 01'FFFF <sub>H</sub> / 02'0000 <sub>H</sub> to 02'7FFF <sub>H</sub> |

| 10         | 2    | 24 KB | 02'8000 <sub>H</sub> to 02'DFFF <sub>H</sub>                                                |

| 1 1        | 3    | 8 KB  | 02'E000 <sub>H</sub> to 02'FFFF <sub>H</sub>                                                |

### **SIEMENS**

### **Operation Modes of the Flash Memory**

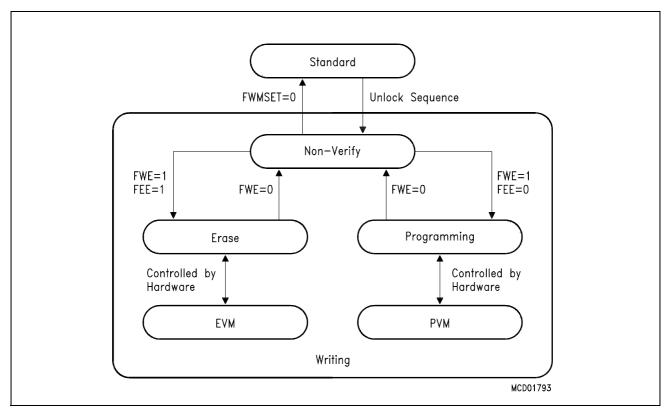

There are two basic operation modes for Flash accesses: The standard and the writing mode. Submodes of the writing mode are the programming, the erase and the non-verify mode.

### Figure 4 Flash Operating Mode Transitions

**In Standard Mode** the Flash memory can be accessed from any memory location (external memory, on-chip RAM or Flash memory) for instruction fetches and data operand reads. Data operand reads may use both direct 16-bit (mnemonic: mem) and indirect (mnemonic: [Rw]) addressing modes. Standard mode does not allow Flash write operations or accesses to the FCR except for the protection activation bit RPROT.

**Note:** When Flash protection is active, data operands can be accessed only by instructions that are executed out of the internal Flash memory and branches to the Flash memory from locations outside are inhibited.

**The Flash Writing Modes** must be entered for programming or erasing the Flash memory. The C167CR-16F enters these modes by a specific key code sequence, called UNLOCK sequence. In writing mode the used addressing mode decides whether the FCR or a Flash memory location is accessed. The FCR can be accessed with any direct access to an even address in the active address space of the Flash memory. Only word operand instructions are allowed for FCR accesses. Accesses to Flash memory locations must use indirect addressing to even addresses.

| direct 16-bit addressing mode: | mem>                | Access to FCR            |

|--------------------------------|---------------------|--------------------------|

| indirect addressing mode:      | [Rw <sub>n</sub> ]> | Access to Flash location |

After entering writing mode the first erase or programming operation must not be started for at least 10  $\mu$ s. This absolute (!) delay time is required to set up the internal high voltage. In general, Flash write operations need a 12 V external  $V_{PP}$  voltage to be applied to the  $V_{PP}$  pin.

It is not possible to erase or to program the Flash memory via code executed from the Flash memory itself. The respective code must reside within the on-chip RAM or within external memory.

When programming or erasing 'on-line' in the target system, some considerations have to be taken: While these operations are in progress, the Flash memory cannot be accessed as usual. Therefore care must be taken that no branch is taken into the Flash memory and that no data reads are attempted from the Flash memory during programming or erasure. If the Flash memory is mapped to segment 0, it must especially be ensured that no interrupt or hardware trap can occur, because this would implicitly mean such a 'forbidden' branch to the Flash memory. Correct Flash operation is not guaranteed in this case.

**The UNLOCK sequence** is a specific key code sequence, which is required to enable the writing modes of the C167CR-16F. The UNLOCK sequence must use identical values (see example below) and the two accesses must not be interrupted:

| MOV  | FCR, Rw <sub>n</sub>                | ;Dummy write to the FCR                        |

|------|-------------------------------------|------------------------------------------------|

| MOV  | [Rw <sub>n</sub> ], Rw <sub>n</sub> | ;Both operands use the same GPR                |

| CALL | cc_UC, WAIT_10                      | ;Delay for 10 $\mu$ s (may be realized also by |

|      |                                     | ; instructions other than a delay loop         |

where  $Rw_n$  can be any word GPR (R0...R15).  $[Rw_n]$  and FCR must point to even addresses within the active address space of the Flash memory.

Note: Data paging and Flash segment mapping, if active, must be considered in this context.

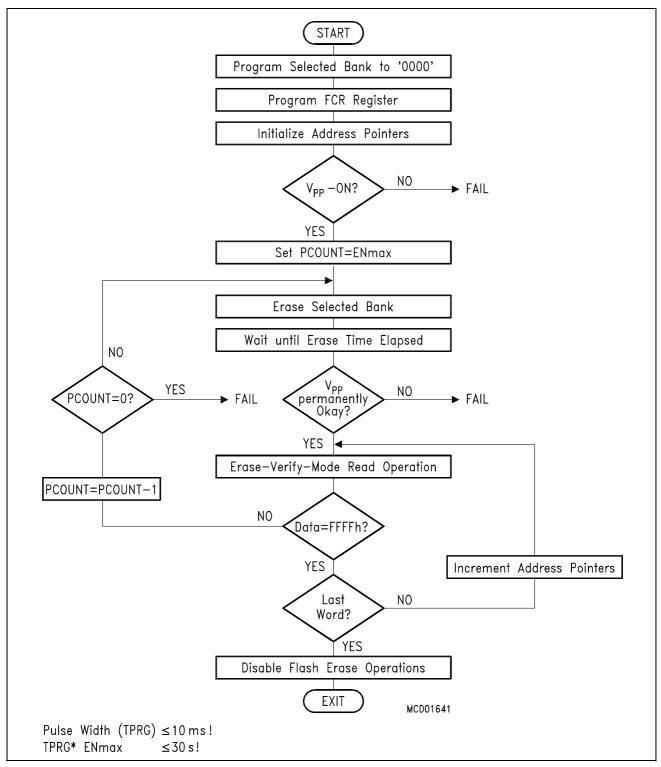

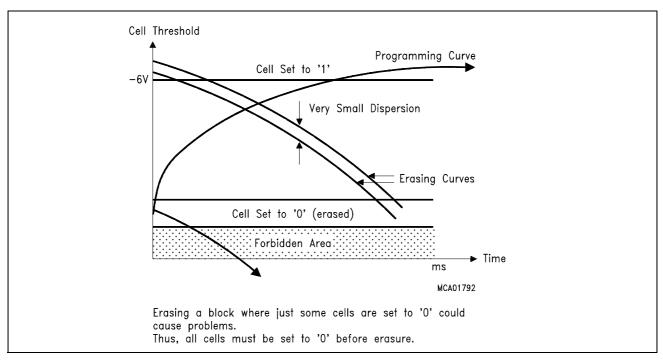

In Flash Erase Mode (FEE='1', FWE='1') the C167CR-16F is prepared to erase the bank selected by the Bank Erase (BE) bit field in the FCR. The width of the erase pulses generated internally is defined by the Internal Flash Timer Clock Control (CKCTL) bit field of the FCR. The maximum number of erase pulses ( $EN_{max}$ ) applied to the Flash memory is determined by software in the Flash erase algorithm. The chosen values for CKCTL and  $EN_{max}$  must guarantee a maximum cumulated erase time of 30 s per bank and a maximum erase pulse width of 10 ms.

The Flash bank erase operation will not start before the erase command is given. This provides additional security for the erase operation. The erase command can be any write operation to a Flash location, where the data and the even address written to must be identical:

### MOV $[Rw_n]$ , $Rw_n$ ; Both operands use the same GPR

Upon the execution of this instruction, the Flash Busy (FBUSY) flag is automatically set to '1' indicating the start of the operation. End of erasure can be detected by polling the FBUSY flag.  $V_{PP}$  must stay within the valid margins during the entire erase process.

At the end of erasure the Erase-Verify-Mode **(EVM)** is entered automatically. This mode allows to check the effect of the erase operation (see description below).

**Note:** Before the erase algorithm can be properly executed, the respective bank of the Flash memory must be programmed to all zeros ('0000<sub>H</sub>').

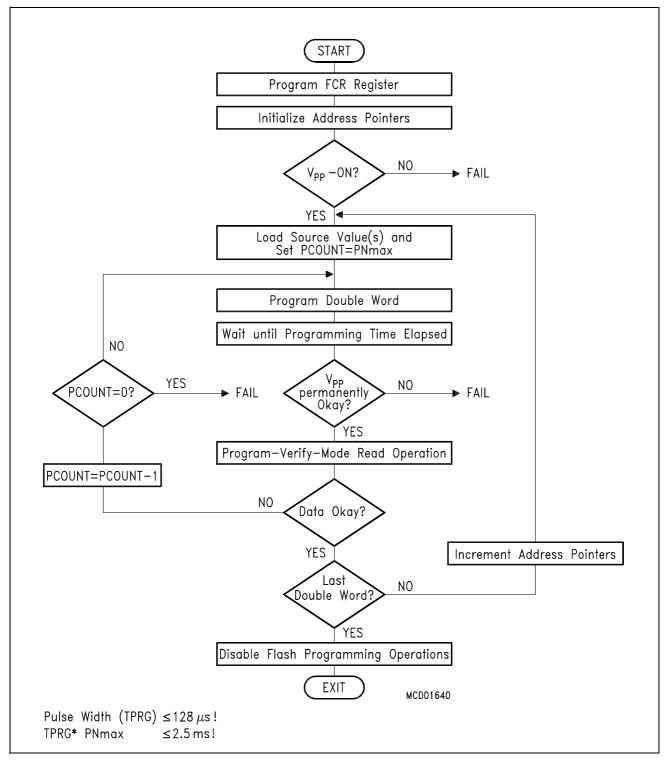

**In Flash Programming Mode** (FEE='0', FWE='1') the C167CR-16F is prepared to program Flash locations in the way specified by the Word or Double Word Write (WDWW) bit in the FCR. The width of the programming pulses generated internally is defined by the Internal Flash Timer Clock Control (CKCTL) bit field of the FCR. The maximum number of programming pulses ( $PN_{max}$ ) applied to the Flash memory is determined by software in the Flash programming algorithm. The chosen values for CKCTL and  $PN_{max}$  must guarantee a maximum cumulated programming time of 2.5 ms per cell and a maximum programming pulse width of 128 µs.