You are here: Foswiki>DaqSlowControl Web>OutdatedPages>DaqNetwork>NewTriggerBusConcept>NewTriggerBusToDo (2008-12-22, JanMichel)Edit Attach

Not the official milestones, but some pragmatic steps:

-- IngoFroehlich - 14 Feb 2006

-- IngoFroehlich - 14 Feb 2006

-- JanMichel - 07 May 2007

-- JanMichel - 07 May 2007

-- JanMichel - 25 Oct 2007

-- JanMichel - 25 Oct 2007

Simulations

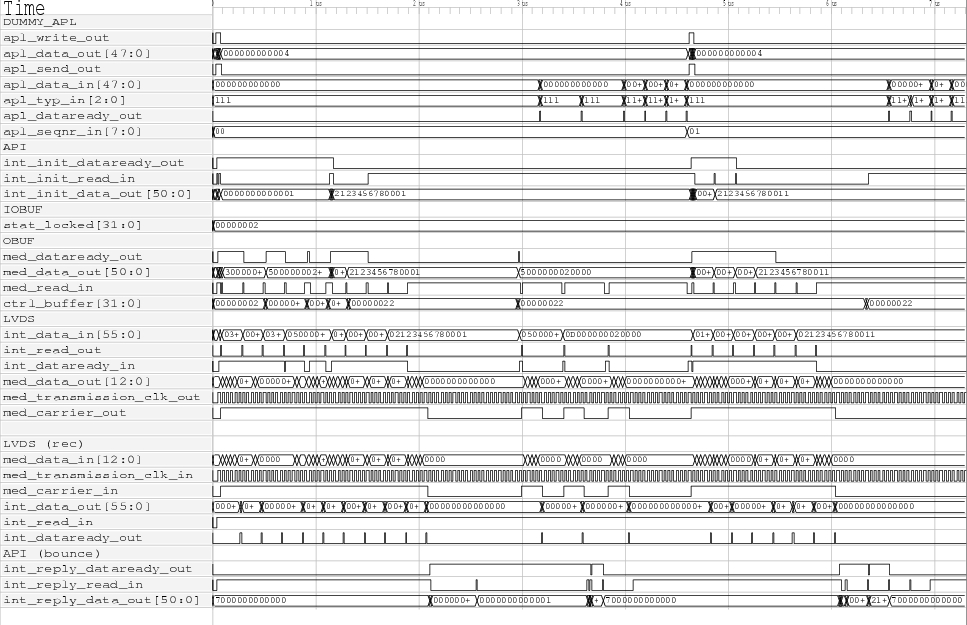

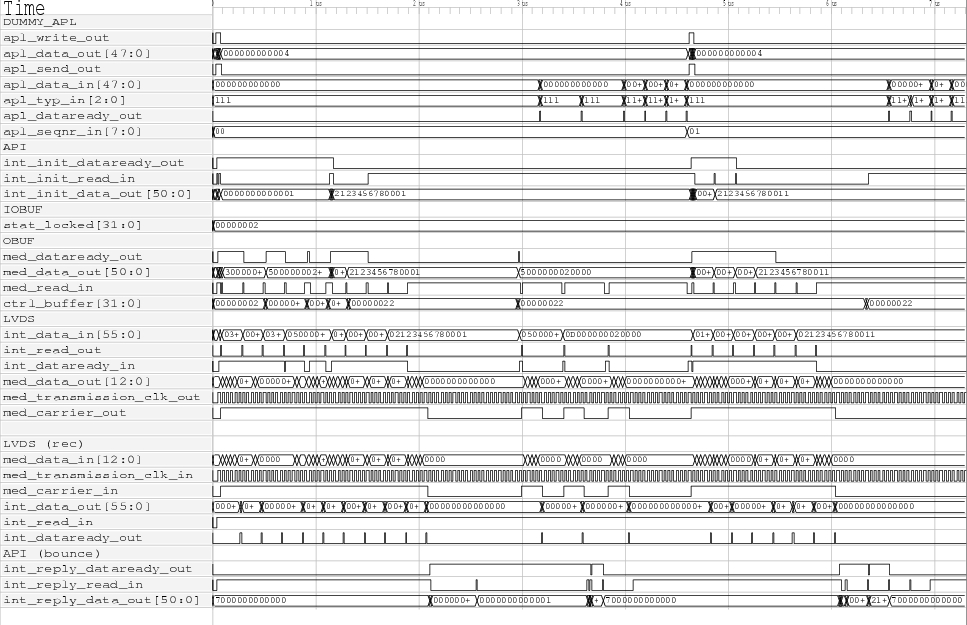

VHDL simulation done by Ingo. First important step is to have a running chain with 2 dummy APLs sending, the complete IOBUFs in between, and the lvds link written by Jan Michel. Simulation seems to be OK (2.3.2007): LVDS is running with 25MHz (slow interface) * lvds chain: -- IngoFroehlich - 14 Feb 2006

-- IngoFroehlich - 14 Feb 2006

Tests with hardware

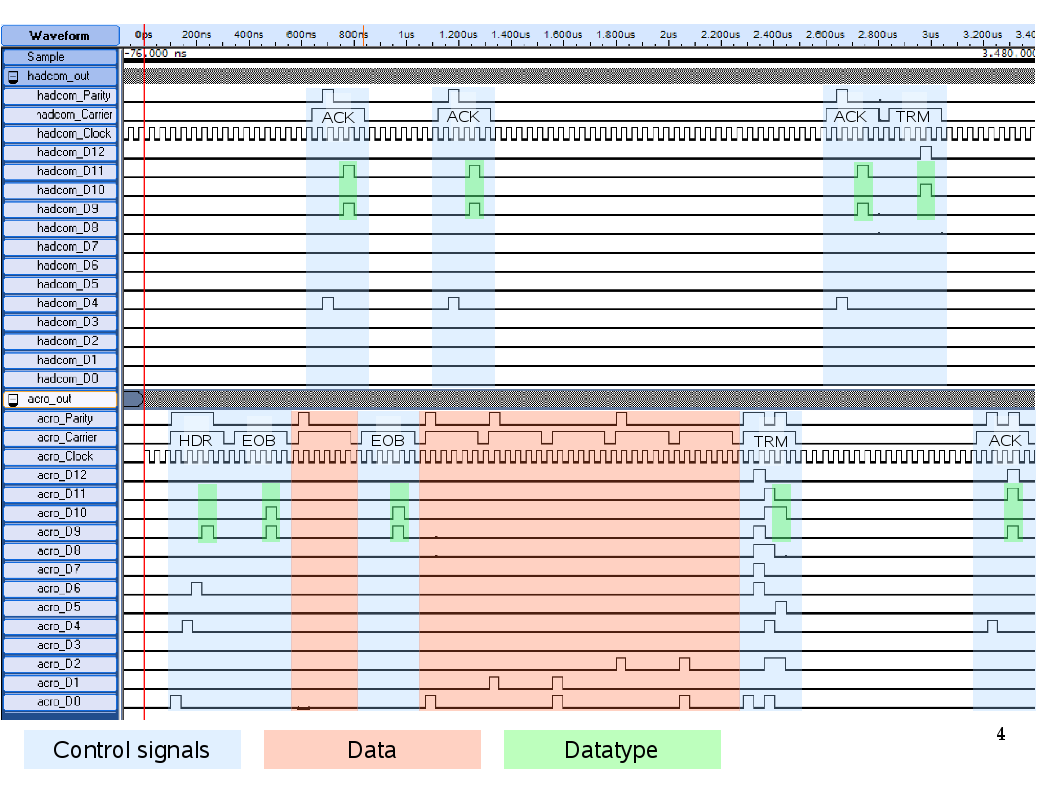

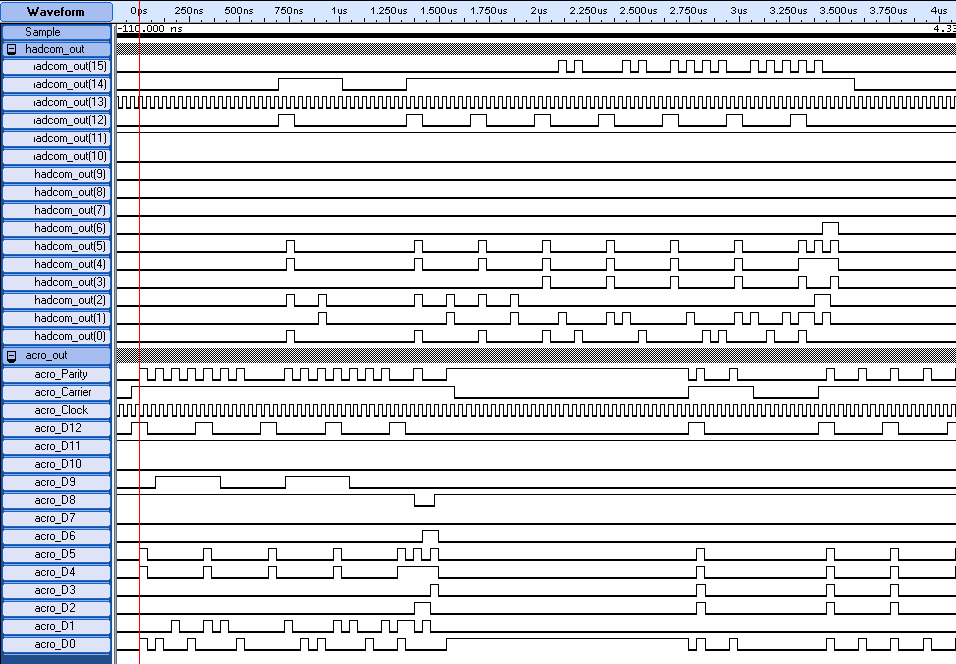

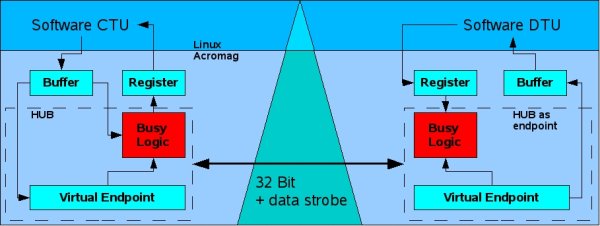

07.05.2007: The communication between the acromag and the TRB test board is running stable now. The acromag contains a simple APL that sends data (it counts from 0 to 5) to the TRB which acknowledges and answers each transfer. Both FPGA are running at 100 MHz while the LVDS transfer has a clock of 25 MHz. -- JanMichel - 07 May 2007

-- JanMichel - 07 May 2007

16 Bit

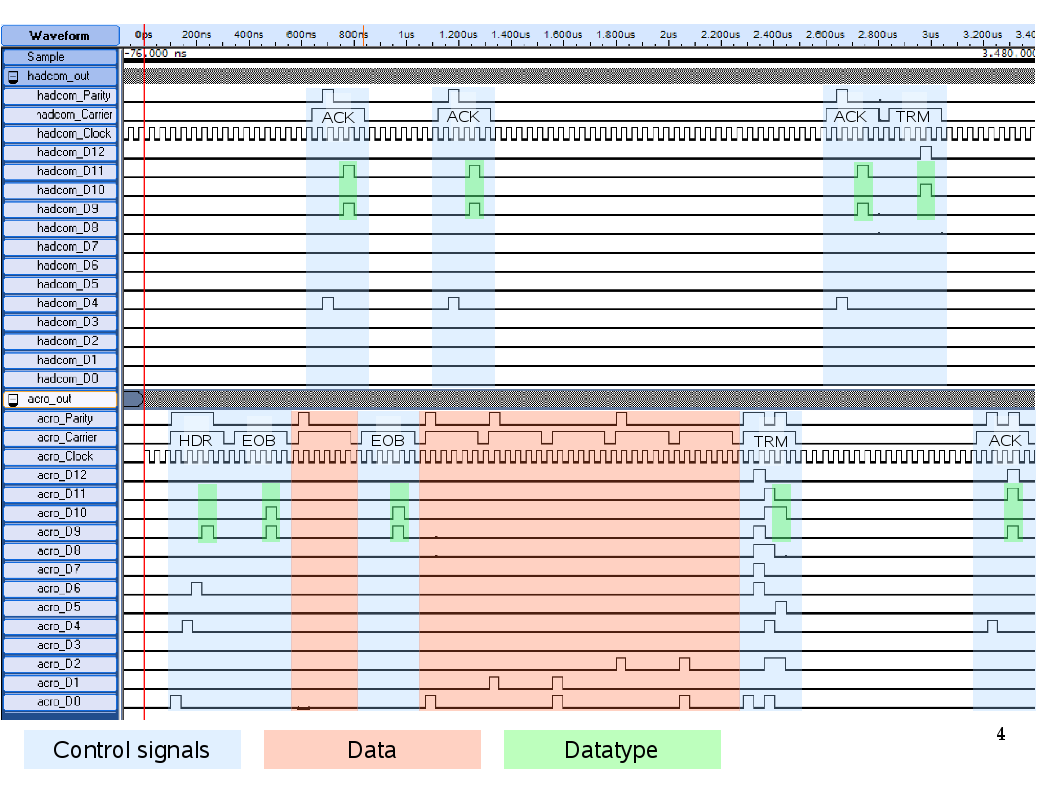

16.10.2007: 16 bit version of the network almost finished. A first test of the new entities in hardware has been done. A sample transfer on a 8Bit LVDS cable with trb_net16:Tests on the optical link and TLK1501

- Done by M. Palka

Loopback test on the AcromagModule

- Get first communication with the acromag design running

- Make a hub base design

- Connect the modules to a loopback device:

- Test interrupts

- Implement software DTU

- Make connection from DTU to software TIP

Connection with the TRB-test board

The TRB test board will have 2 optical links, one SCSI link to connect the AcromagModule and might serve as an old-to-new converter. In this sense, it is a TRB-Net-HubEdit | Attach | Print version | History: r8 < r7 < r6 < r5 | Backlinks | View wiki text | Edit wiki text | More topic actions

Topic revision: r8 - 2008-12-22, JanMichel

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Ideas, requests, problems regarding Foswiki Send feedback | Imprint | Privacy Policy (in German)

Ideas, requests, problems regarding Foswiki Send feedback | Imprint | Privacy Policy (in German)